There’s a reason for rules in PCB design, but some of them can be disregarded if effort is applied to mitigate the problem(s) the rule was intended to prevent. This stack-up, if implemented correctly is one such example.

The critical part usually is that the board can warp during assembly. This happens because of a mismatch in the amount / position of copper on the relevant layers. If we make the assumption that PWR and GND layers will be close to 100% copper, then the mismatch here is layer 3 (PWR) and layer 6 (signal). So the question is whether we can make a signal layer look more like a plane, or a plane layer look more like a signal layer? Adding copper to the signal layer is not likely to be a big problem as long as it is connected to something sensible (like GND) and is well stitched in to the other GND planes. Depending on how much coverage on the signal layer can be achieved (which might not be as high as might be hoped), the next trick is to remove copper from the plane layer. This is easily done by turning it into a hashed plane. Tweak the size of the apertures in the grid to match the total coverage percentage on the signal layer and that should be fine.

Of course, the rest of the symmetry should be maintained in terms of the thicknesses of cores and prepregs.

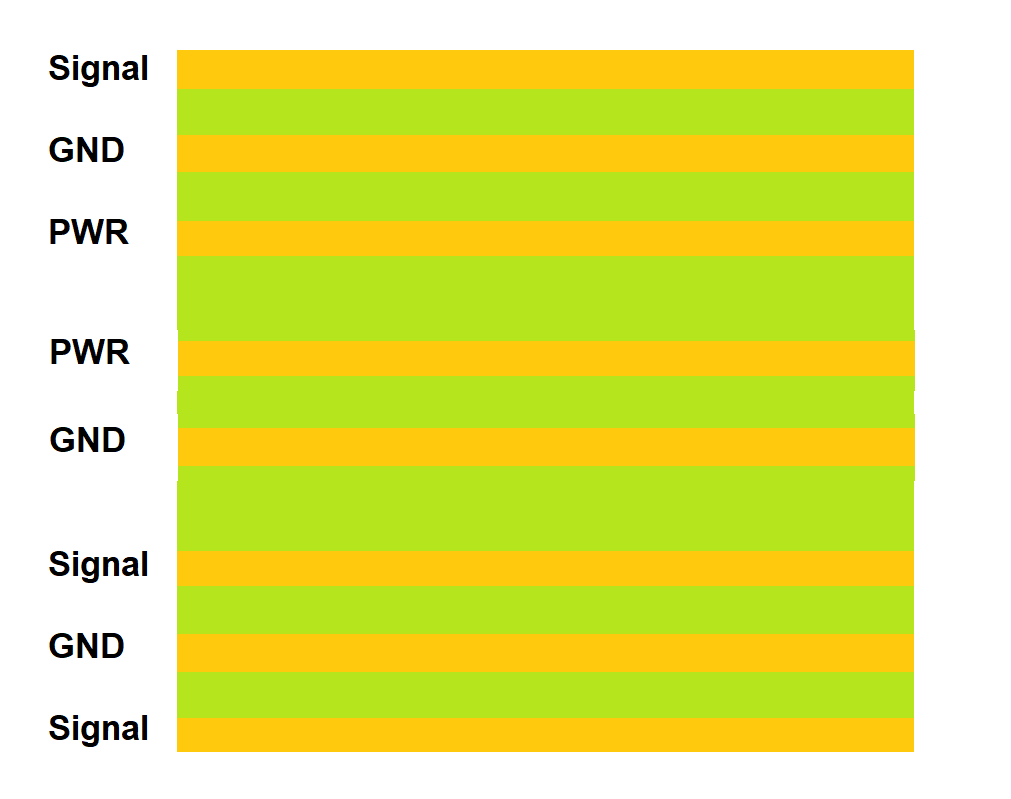

It’s now time to consider the other matters. Let’s take return paths first. Every signal layer is adjacent to one or two GND layers (and nothing else is adjacent to them). This is a great start. Layer changes just require a GND plane stitching via(s) in the vicinity of the signal via and problem solved.

For the PWR layers, they are sandwiched between GND layers, but when you look at either of the PWR layers, each PWR layer references both a GND layer and the other PWR layer. Therefore some signal flow will be induced by PWR-L3 in PWR-L4, and vice-versa. This is crosstalk between PWR layers and is not desireable. However, it is easy to do something to minimise this. If the spacing between L2 (GND) and L3 (PWR) is made small relative to the spacing between L3 (PWR) and L4 (PWR), it follows that the bulk of the coupling will be between PWR and GND, and much less between PWR and PWR.

If this is the case, then by symmetry, the spacing between L6 (Signal) and L7 (GND) must also be small. This is good if this is a high signal density design because it means that thin traces will probably give sensible impedances allowing for high routing density. If these traces are thin, then having fairly thin traces on the outer layer makes sense, and this points to making the spacing between L1 (signal) and L2 (GND) also be narrow (and likewise L7 (GND) to L8 (signal). So it appears that the stackup to aim for should have these thicknesses:

L1-L2 = narrow

L2-L3 = narrow

L3-L4 = wide

L4-L5 = narrow

L5-L6 = wide

L6-L7 = narrow

L7-L8 = narrow

This should ensure that return paths are as close to ideal as is reasonably possible. GND vias are all that are needed to provide the return paths for all signals. Power crosstalk is minimised by distance (reduce coupling). Signal crosstalk is no different to how it would be if you added more GND layers. As a consequence, the EMI should be minimal. It seems like the manufacturability should be good. It is a little bit unusual so the PCB price may not be as cheap as other 8-layer boards, but it doesn’t look as though it should cost too much. The only other thing worth adding is that if L3 (PWR) is now a perforated layer to match the percentage copper weight of L6 (signal) the reduction in the amount of copper on L3 suggests putting the lower current supplies on this layer if possible.

In principle, this asymmetric layer stack looks as though it is a sound engineering solution. The only other remark is to verify with your PCB house that they can make it without any serious issues.